## University of Colorado, Boulder **CU Scholar**

Electrical, Computer & Energy Engineering Graduate Theses & Dissertations

Electrical, Computer & Energy Engineering

Spring 4-1-2010

## Digital Control Techniques for Single-Phase Power Factor Correction Rectifiers

Barry A. Mather *University of Colorado at Boulder*, matherb@gmail.com

Follow this and additional works at: https://scholar.colorado.edu/ecen\_gradetds

Part of the Electrical and Electronics Commons, Electronic Devices and Semiconductor

Manufacturing Commons, and the Power and Energy Commons

#### Recommended Citation

Mather, Barry A., "Digital Control Techniques for Single-Phase Power Factor Correction Rectifiers" (2010). *Electrical, Computer & Energy Engineering Graduate Theses & Dissertations*. 9. https://scholar.colorado.edu/ecen\_gradetds/9

This Dissertation is brought to you for free and open access by Electrical, Computer & Energy Engineering at CU Scholar. It has been accepted for inclusion in Electrical, Computer & Energy Engineering Graduate Theses & Dissertations by an authorized administrator of CU Scholar. For more information, please contact cuscholaradmin@colorado.edu.

## Digital Control Techniques for Single-Phase Power Factor Correction Rectifiers

by

#### Barry A. Mather

B.S., University of Wyoming, 2001

M.S., University of Wyoming, 2004

M.S., University of Colorado, 2008

A thesis submitted to the

Faculty of the Graduate School of the

University of Colorado in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

Department of Electrical, Computer and Energy Engineering \$2010\$

# This thesis entitled: Digital Control Techniques for Single-Phase Power Factor Correction Rectifiers written by Barry A. Mather has been approved for the Department of Electrical, Computer and Energy Engineering

| Professor Dragan Maksimović | <u></u> |

|-----------------------------|---------|

| Ü                           |         |

|                             |         |

| Professor Regan Zane        |         |

|                             |         |

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards of scholarly work in the above mentioned discipline.

Mather, Barry A. (Ph.D., Electrical Engineering)

Digital Control Techniques for Single-Phase Power Factor Correction Rectifiers

Thesis directed by Professor Dragan Maksimović

Tightening governmental regulations and industry standards for input current harmonics and input power factor correction (PFC) of common electronic devices such as servers, computers and televisions continues to increase the need for high-performance, low-cost power factor correction controllers. In response to this need, digital non-linear carrier (DNLC) PFC control has been developed and is presented in this thesis. DNLC PFC control offers many unique advantages over existing PFC control techniques in terms of design simplicity, low harmonic current shaping over a wide load range including CCM and DCM operation and a reliable, inexpensive digital implementation based on low-resolution analog-to-digital converters (A/D's) and digital pulse width modulator (DPWM). Implementation of the controller requires no microcontroller or digital signal processor (DSP) programming, and is well suited for a simple, low-cost integrated-circuit realization. DNLC PFC control is derived and analyzed for single-phase universal input PFC boost rectifiers. Further analysis of the operation of digitally controlled PFC rectifiers leads to the development of voltage loop compensator design constraints that avoid limit-cycling of the voltage loop. It is demonstrated that voltage loop limit-cycling is unavoidable when using traditional PFC control techniques under certain output loading conditions. However, it is also shown that voltage loop limit-cycling is avoidable under the same operating conditions when a DNLC PFC controller is implemented. Additionally, a unique output voltage sensing A/D is also developed that improves the PFC voltage loop transient response to load transients when paired with the DNLC PFC controller. Experimental results are shown for a 300W universal input boost PFC rectifier.

#### Acknowledgements

Thanks are due foremost to my advisor, Professor Dragan Maksimović, for teaching me how to perform research. His guidance and encouragement throughout my graduate studies have enhanced the entire learning experience. Thanks also to Professors Regan Zane and Robert Erickson for their excellent instruction in the areas of mixed-signal electronics and power electronics respectively.

Thank you to Professor Baylor Fox-Kemper for helping me improve my technical writing and reviewing skills. Professor Stanislaw Legowski, thank you for starting me down the path of graduate studies.

I would also like to acknowledge and thank Isaac Cohen and Larry Wofford of Texas Instruments for their continuous interest, support and advice regarding my research project.

Finally, I would like to thank my colleagues at the Colorado Power Electronics Center (CoPEC), my wife and my family for their patient help and gracious support.

## Contents

## Chapter

| 1 | Intro | oduction | n                                                            | 1  |

|---|-------|----------|--------------------------------------------------------------|----|

| 2 | Bacl  | kground  | l                                                            | 4  |

|   | 2.1   | Power    | Factor Correction and Applicable Standards                   | 4  |

|   |       | 2.1.1    | Power Factor Correction and Harmonic Currents                | 5  |

|   |       | 2.1.2    | Harmonic Current Limits and Power Factor Standards           | 9  |

|   | 2.2   | Boost    | Converter Fundamentals                                       | 12 |

|   | 2.3   | Boost    | Converter as a PFC Rectifier                                 | 14 |

|   | 2.4   | Boost    | PFC Rectifiers with Analog Control                           | 15 |

|   | 2.5   | Digita   | l Control of Switched-mode Power Converters                  | 17 |

|   |       | 2.5.1    | Digital Average Current Mode PFC Rectifiers                  | 20 |

|   |       | 2.5.2    | Predictive Control                                           | 25 |

|   |       | 2.5.3    | Inductor Charge Control                                      | 26 |

|   |       | 2.5.4    | Hybrid PFC Control                                           | 27 |

| 3 | A Si  | mple D   | rigital Power Factor Correction Rectifier Controller         | 29 |

|   | 3.1   | Deriva   | ation of the Basic Digital Nonlinear Carrier PFC Control Law | 31 |

|   |       | 3.1.1    | Stability of the Current Control Loop                        | 33 |

|   |       | 3.1.2    | Operation and Stability at Light Loads                       | 36 |

|   | 3.2   | Voltag   | ge Regulation and Power Control                              | 36 |

|   |       | 3.2.1    | Power Control via $u[n]$                                                        | 38 |

|---|-------|----------|---------------------------------------------------------------------------------|----|

|   |       | 3.2.2    | Power Control via $d_{max}[k]$                                                  | 39 |

|   |       | 3.2.3    | $\Sigma\Delta$ Modulation of $u[n]$                                             | 43 |

|   | 3.3   | System   | Implementation                                                                  | 44 |

|   |       | 3.3.1    | DNLC PFC Current Controller Bandwidth                                           | 45 |

|   |       | 3.3.2    | Quantization issues                                                             | 46 |

|   | 3.4   | Experi   | mental Waveforms                                                                | 49 |

|   |       | 3.4.1    | Operation at High and Moderate Power                                            | 49 |

|   | 3.5   | Chapte   | er Summary                                                                      | 52 |

| 4 | Qua   | ntizatio | n Effects and Limit Cycling in Digitally Controlled Single-Phase PFC Rectifiers | 53 |

|   | 4.1   | Digital  | Control of Single-Phase Boost PFC Rectifiers                                    | 54 |

|   | 4.2   | Outpu    | t Voltage Sampling                                                              | 57 |

|   | 4.3   | Power    | Command Quantization                                                            | 61 |

|   |       | 4.3.1    | Voltage Loop Limit Cycling in PFC Rectifiers with Digital Average Current       |    |

|   |       |          | Mode Control                                                                    | 64 |

|   |       | 4.3.2    | Voltage Loop Limit Cycling in PFC Rectifiers with Digital NLC Control           | 67 |

|   | 4.4   | Chapte   | er Summary                                                                      | 69 |

| 5 | Sing  | le Com   | parator A/D Converter for Output Voltage Sensing of Single Phase PFC Recti-     |    |

|   | fiers |          |                                                                                 | 70 |

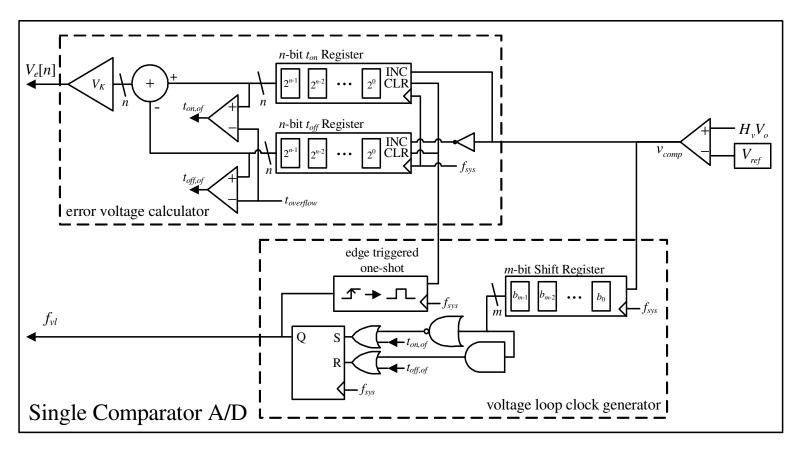

|   | 5.1   | Single-  | Comparator A/D (SCA/D) Operation                                                | 72 |

|   |       | 5.1.1    | SCA/D Concept                                                                   | 72 |

|   |       | 5.1.2    | Relationship Between $d_{comp}$ and $V_e$                                       | 74 |

|   |       | 5.1.3    | Calculating the Error Voltage                                                   | 77 |

|   |       | 5.1.4    | Generation of $f_{vl}$                                                          | 79 |

|   |       | 5.1.5    | Implementation of the SCA/D $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$      | 81 |

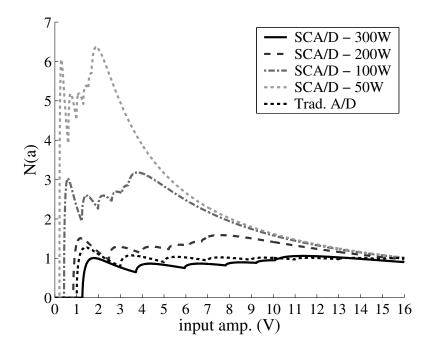

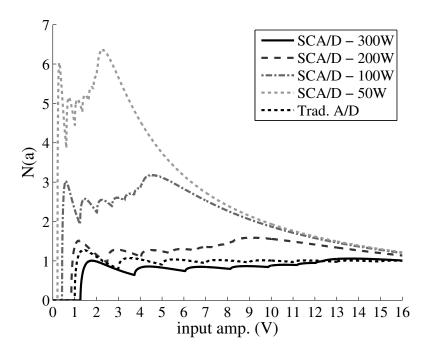

|   |       | 5.1.6    | Implemented SCA/D's Describing Function and the Effects of Saturation           | 81 |

|   | 5.2  | Power    | Feedforward                                                 | 83  |

|---|------|----------|-------------------------------------------------------------|-----|

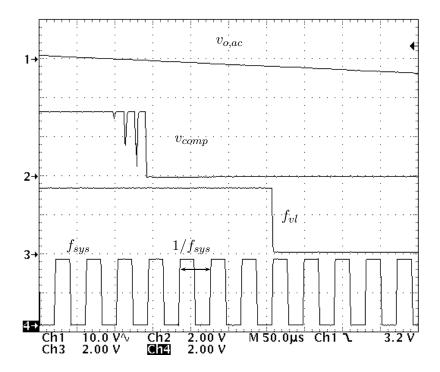

|   | 5.3  | Experi   | imental Results                                             | 85  |

|   |      | 5.3.1    | Comparator Signal Conditioning                              | 86  |

|   |      | 5.3.2    | Outer Voltage Loop Bandwidth Improvement                    | 87  |

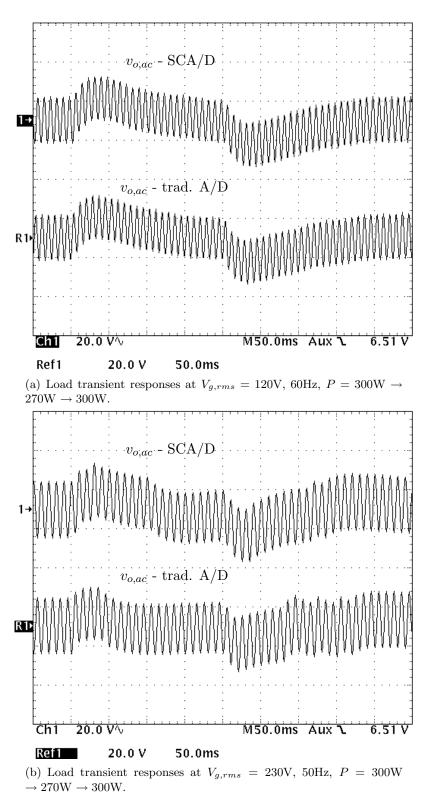

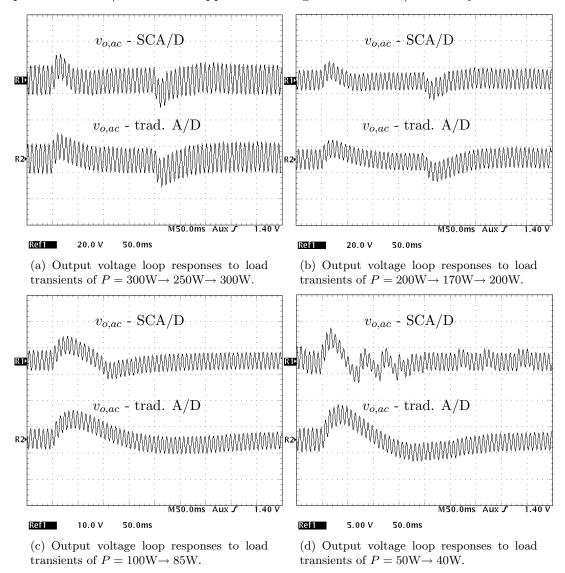

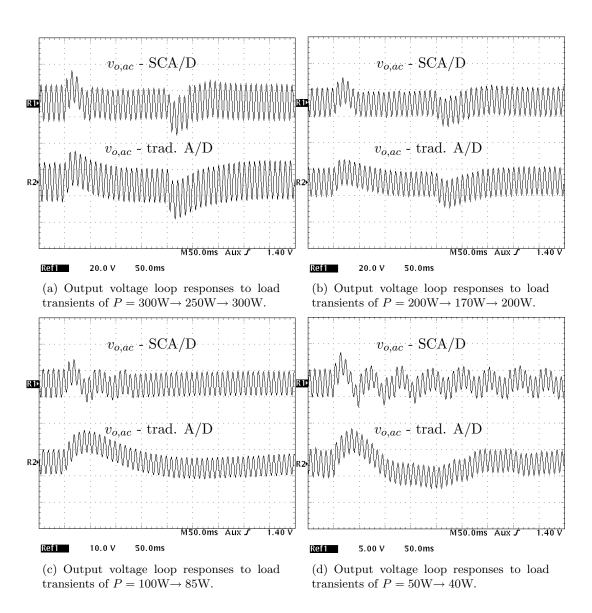

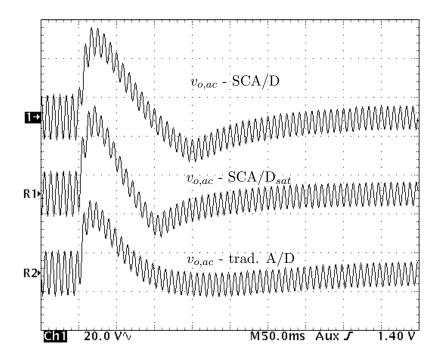

|   |      | 5.3.3    | Load Transient Responses                                    | 91  |

|   | 5.4  | Chapt    | er Summary                                                  | 97  |

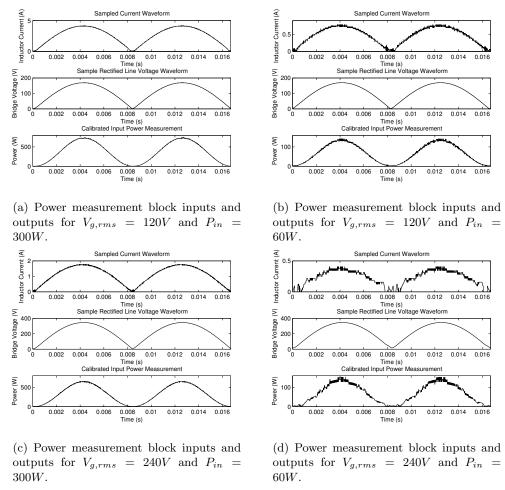

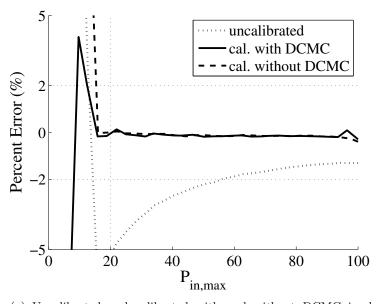

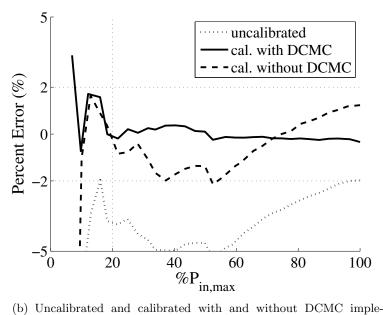

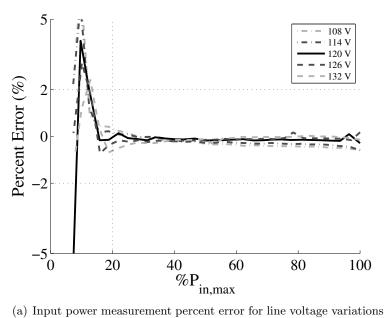

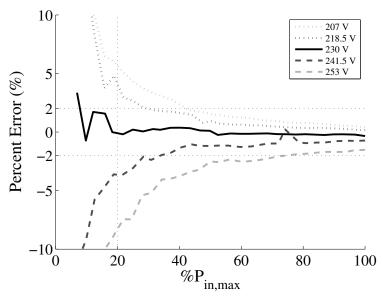

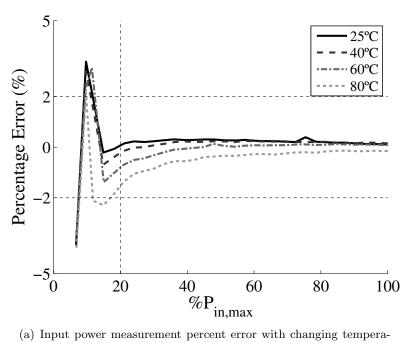

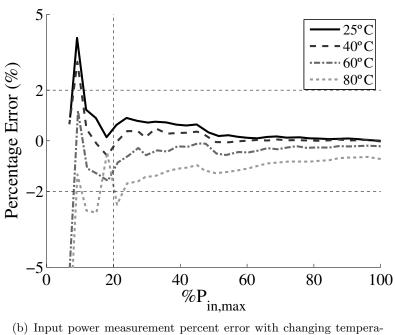

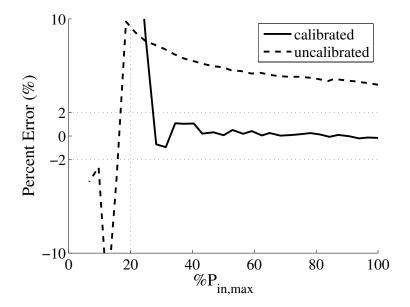

| 6 | PFC  | Input    | Power Measurement Using Data Collected for Control Purposes | 98  |

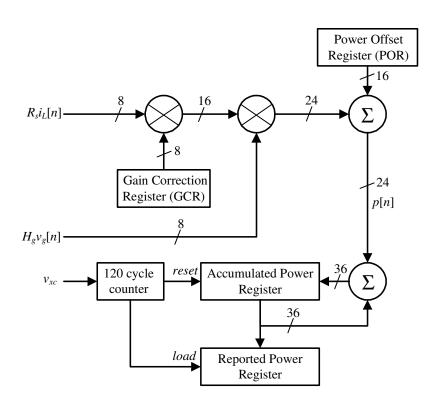

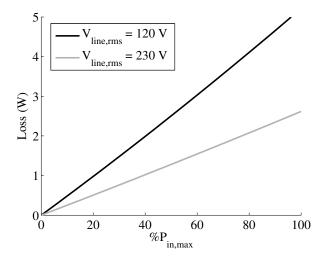

|   | 6.1  | Power    | Measurement Errors and Calibration                          | 100 |

|   |      | 6.1.1    | Indirect Input Power Measurement Using a Look-up Table      | 101 |

|   |      | 6.1.2    | Gain Correction and Power Offset Registers                  | 103 |

|   |      | 6.1.3    | Current Sense Correction During DCM Operation               | 104 |

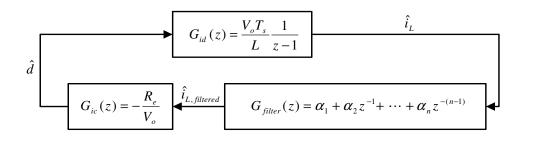

|   | 6.2  | Input    | Power Measurement Techniques Using Digital Control Data     | 106 |

|   |      | 6.2.1    | DACM PFC Rectifier Technique                                | 106 |

|   |      | 6.2.2    | DNLC PFC Rectifier Technique                                | 108 |

|   |      | 6.2.3    | Output Current Sensing Technique                            | 110 |

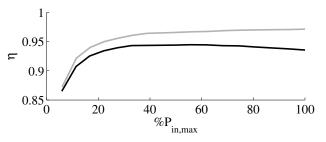

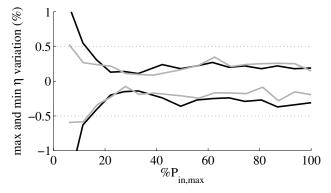

|   | 6.3  | Experi   | imental Results                                             | 111 |

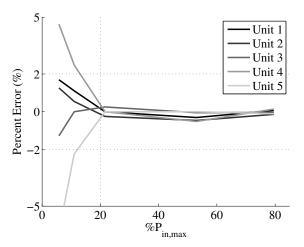

|   |      | 6.3.1    | DACM PFC Rectifier Technique                                | 111 |

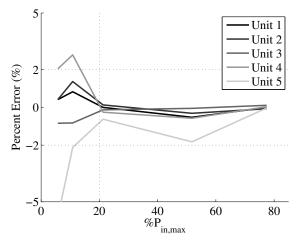

|   |      | 6.3.2    | DNLC PFC Rectifier Technique                                | 118 |

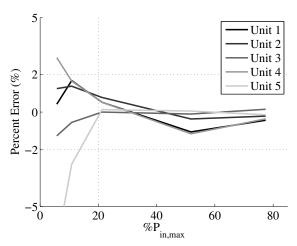

|   |      | 6.3.3    | $I_o$ Sensing Technique                                     | 118 |

|   | 6.4  | Chapt    | er Summary                                                  | 119 |

| 7 | Cone | clusions | $\mathbf{S}$                                                | 122 |

|   | 7.1  | Contri   | butions:                                                    | 122 |

|   | 7.2  | Direct   | ions for future research:                                   | 125 |

|                                                                  | viii |

|------------------------------------------------------------------|------|

| Bibliography                                                     | 129  |

|                                                                  |      |

| Appendix                                                         |      |

| A DNLC Control Law Extension with Increased Current Filter Order | 134  |

## Tables

## Table

| 2.1 | Minimum PF requirements for popular certification programs                               | 11  |

|-----|------------------------------------------------------------------------------------------|-----|

| 3.1 | Current filter coefficients for extending the $K_{crit}$ stability range of the DNLC PFC |     |

|     | controller                                                                               | 35  |

| 3.2 | Prototype DNLC PFC parameters                                                            | 45  |

| 3.3 | THD measurements for various current A/D resolutions, 9-bit DPWM, $P=300\mathrm{W}.$ .   | 48  |

| 3.4 | Power factor measurements for the DNLC PFC with a 4-bit DPWM with a 5-bit                |     |

|     | $\Sigma \Delta_d$ and an 8-bit current A/D                                               | 51  |

| 4.1 | Derived control to output transfer functions for the DNLC and DACM PFC controllers.      | 64  |

| 5.1 | SCA/D PFC stage parameters                                                               | 72  |

| 5.2 | Control-to-output dc gain and dc loop gain of the voltage loop when the SCA/D is         |     |

|     | implemented                                                                              | 84  |

| 5.3 | Comparison of closed-loop bandwidth and phase margin of digital outer voltage loops      |     |

|     | implemented using either a SCA/D or a traditional A/D and NLC current control            | 89  |

| 5.4 | Comparison of closed-loop bandwidth and phase margin of digital outer voltage loops      |     |

|     | implemented using either a SCA/D or a traditional A/D and ACM current control            | 91  |

| 6.1 | Overview of input power measurement techniques                                           | 100 |

| 6.2 | Input power measurement PFC stage parameters                                             | 111 |

| A.1 | Extension of the $K_{crit}$ stability range of the DNLC PFC controller using up to eight |

|-----|------------------------------------------------------------------------------------------|

|     | current filter coefficients                                                              |

## Figures

## Figure

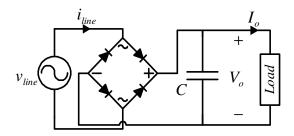

| 2.1  | Uncontrolled full bridge rectifier with a large output capacitor                            | 6  |

|------|---------------------------------------------------------------------------------------------|----|

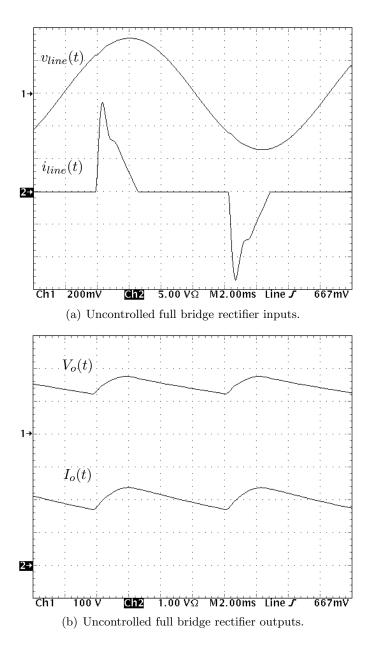

| 2.2  | Uncontrolled full bridge rectifier input and output waveforms                               | 7  |

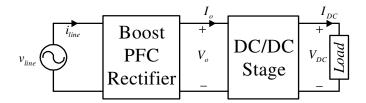

| 2.3  | Typical power supply block diagram                                                          | 12 |

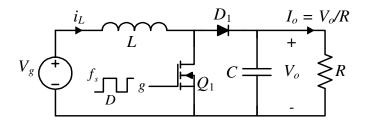

| 2.4  | DC-DC boost converter                                                                       | 13 |

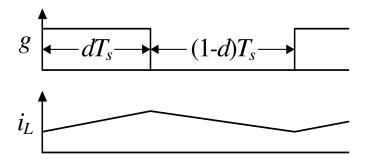

| 2.5  | DC-DC boost converter characteristic waveforms                                              | 13 |

| 2.6  | Basic schematic of a boost PFC rectifier                                                    | 14 |

| 2.7  | Analog average current mode PFC block diagram                                               | 15 |

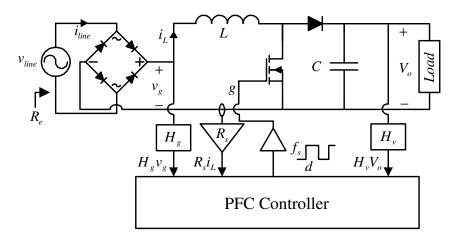

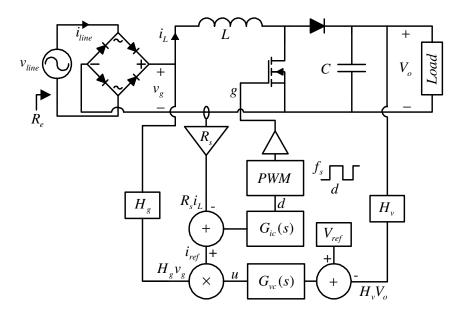

| 2.8  | Digital average current mode PFC boost rectifier                                            | 21 |

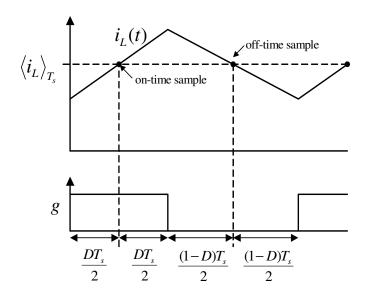

| 2.9  | Digital sampling of the average inductor current                                            | 21 |

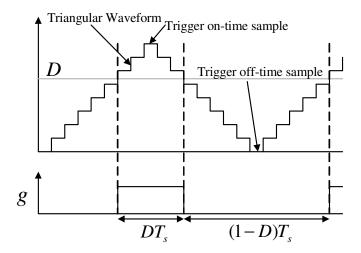

| 2.10 | Sampling during the on or off-time using a triangular DPWM                                  | 22 |

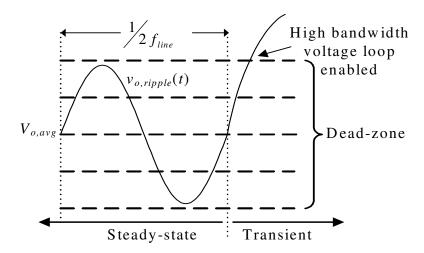

| 2.11 | Pictorial diagram of dead-zone implementation and transient detection                       | 24 |

| 2.12 | Hybrid ACM PFC boost rectifier with a digitally controlled variable resistor $\mathrm{D/A}$ |    |

|      | implementation                                                                              | 27 |

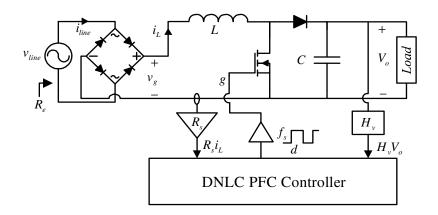

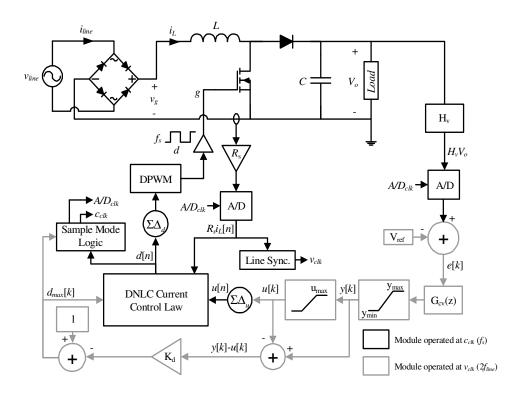

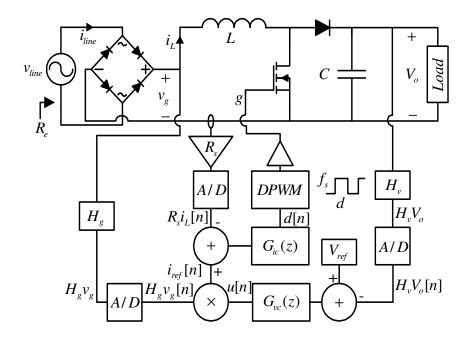

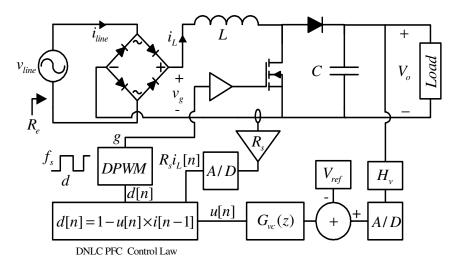

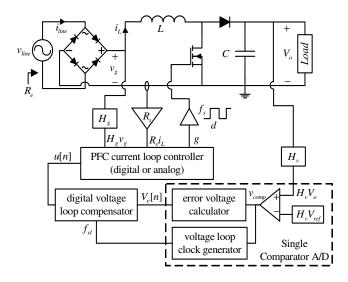

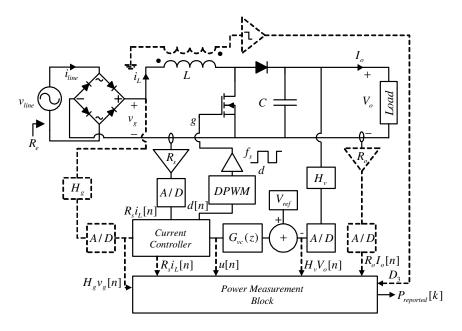

| 3.1  | DNLC controlled PFC boost rectifier                                                         | 31 |

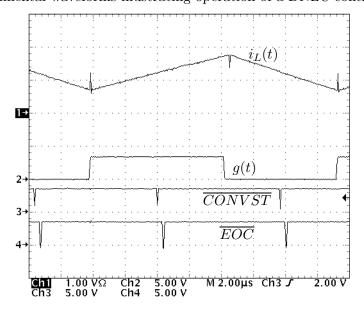

| 3.2  | Experimental waveforms illustrating the operation of the boost PFC with DNLC                |    |

|      | PFC current control law (3.3)                                                               | 32 |

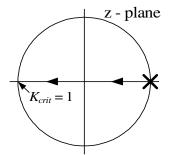

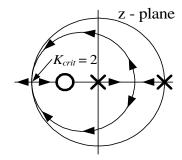

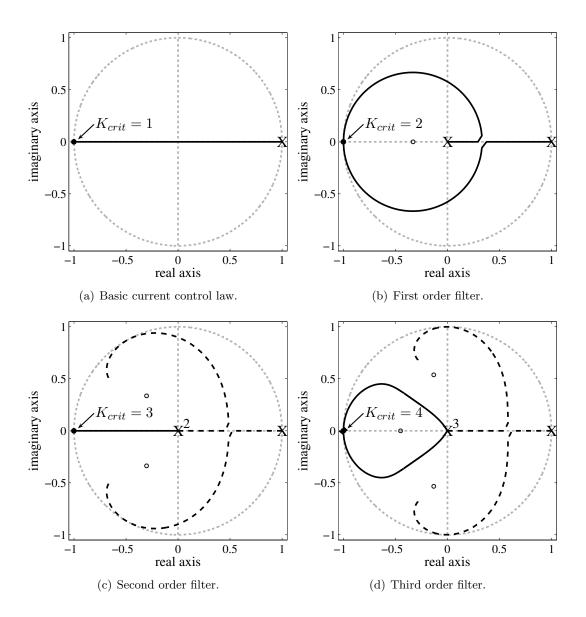

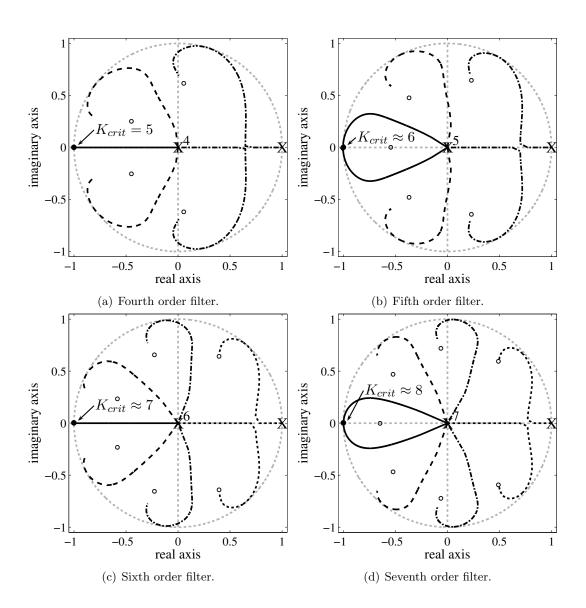

| 3.3  | Root-locus plots of closed loop system poles for two implementations of the DNLC            |    |

|      | PFC controller                                                                              | 33 |

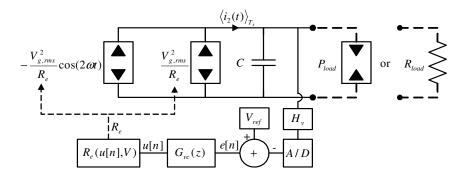

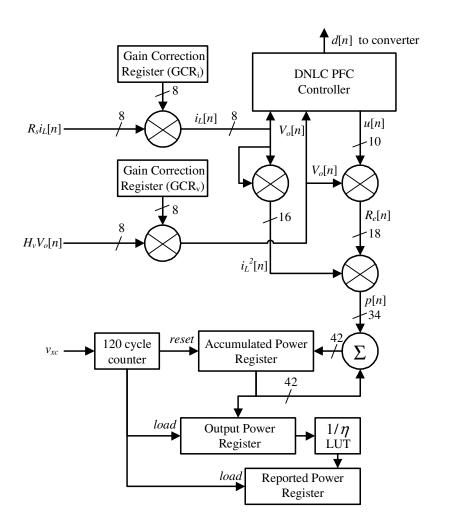

| 3.4  | Complete DNLC PFC controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

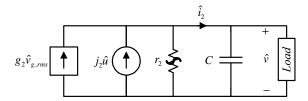

| 3.5  | Averaged small signal model of the DNLC controlled boost PFC output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38         |

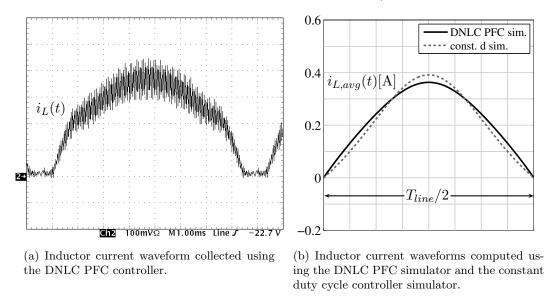

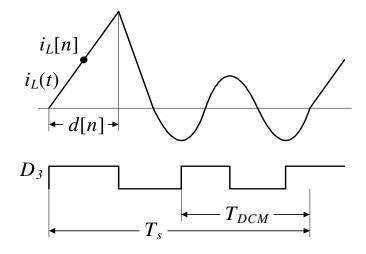

| 3.6  | Comparison of experimental and simulated inductor current waveforms in DCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|      | always operation, $P = 30$ W, $V_{g,rms} = 120$ V, $60$ Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40         |

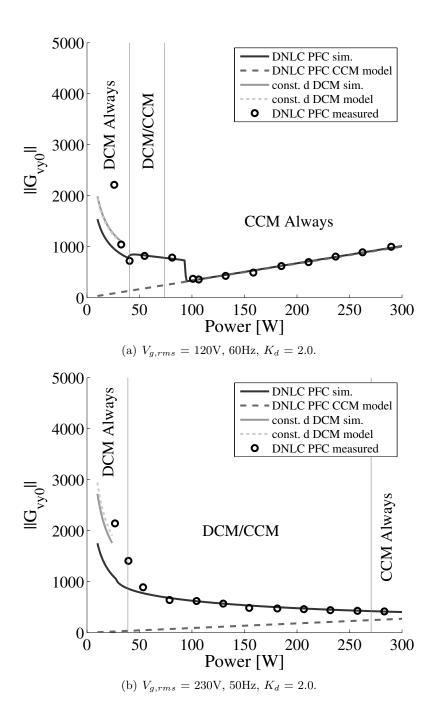

| 3.7  | Control-to-output transfer function dc gains of the outer voltage loop for $V_{g,rms} =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|      | 120V, 60Hz, and 230V, 50Hz, and $d_{max}$ control gain $K_d=2.0$ , basic DNLC PFC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|      | control law given by (3.3), $u_{max} = 0.4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41         |

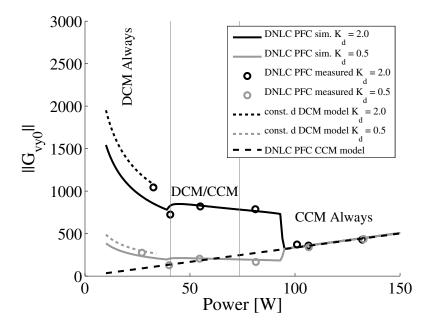

| 3.8  | Outer voltage loop control-to-output dc transfer function gain for $V_{g,rms}=120\mathrm{V},$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|      | 60Hz, and $d_{max}$ control loop gains of $K_d=2.0$ and $0.5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43         |

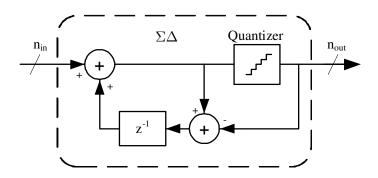

| 3.9  | Error-feedback configuration of a first-order $\Sigma\Delta$ modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44         |

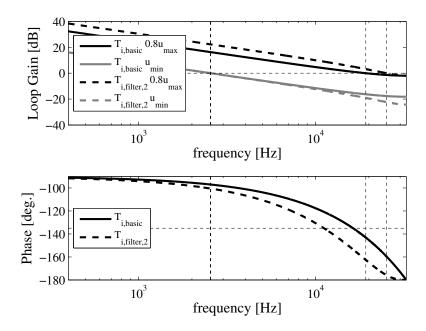

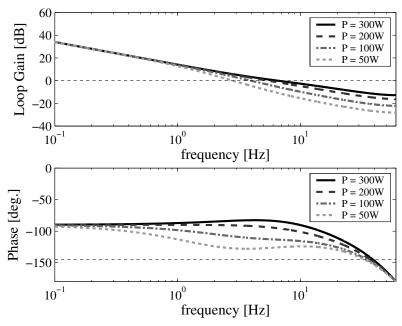

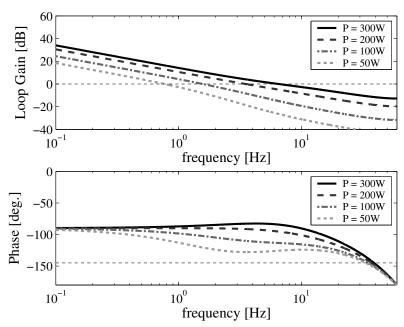

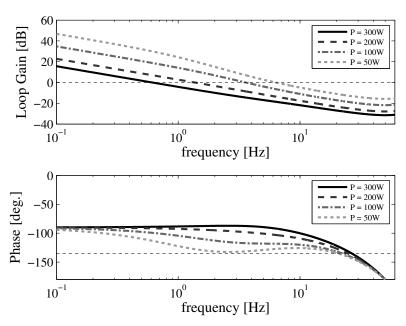

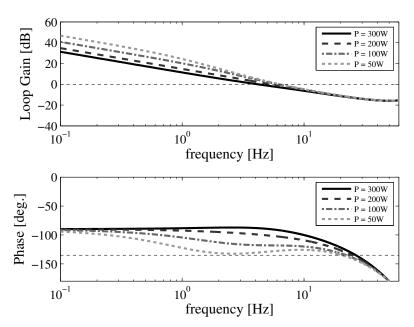

| 3.10 | Current loop gain magnitude and phase of the basic DNLC control law given in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |

|      | (3.3) and the two sample current filter DNLC control law at steady state operating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |

|      | power levels corresponding to $u_{min}$ and $0.8u_{max}$ for a PFC rectifier with power stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|      | parameters given in Table 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46         |

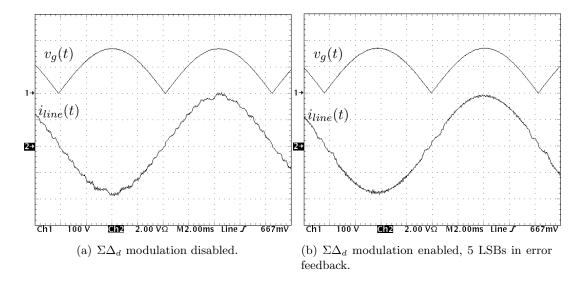

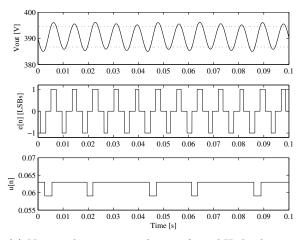

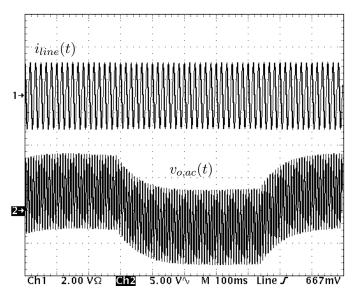

| 3.11 | Converter waveforms with and without $\Sigma\Delta$ modulation of the duty cycle command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|      | enabled, $P=300\mathrm{W},V_{g,rms}=120\mathrm{V},60\mathrm{Hz},4\text{-bit DPWM},8\text{-bit current sensing A/D}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47         |

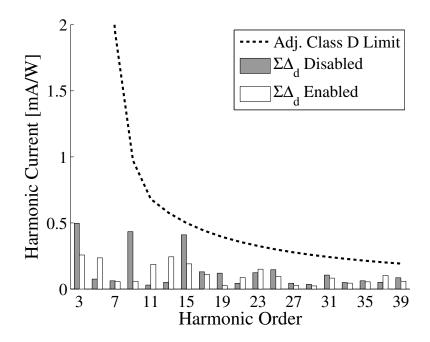

| 3.12 | Harmonic current levels with and without $\Sigma \Delta_d$ dithering implemented, $P=300\mathrm{W},$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|      | $V_{g,rms}=120\mathrm{V},60\mathrm{Hz},3\text{-bit DPWM},4\text{-bit current sensing A/D.}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49         |

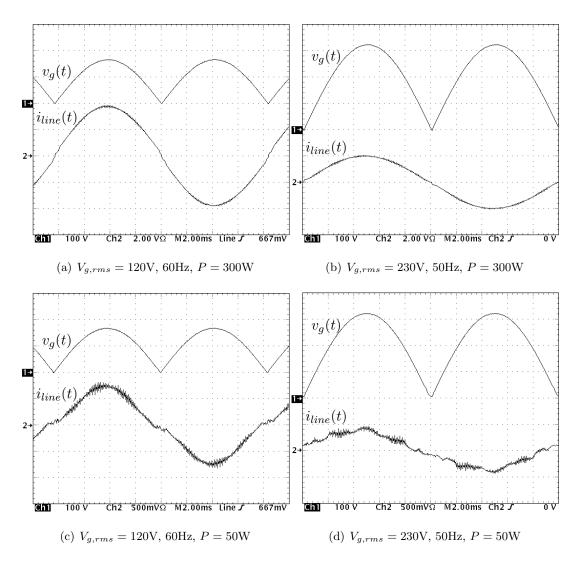

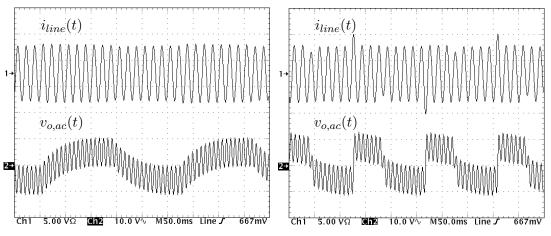

| 3.13 | Experimental DNLC PFC waveforms, $i_{line}(t)$ and $v_g(t)$ , for $P=300\mathrm{W}$ and $50\mathrm{W}$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |

|      | $V_{g,rms}=120\mathrm{V},60\mathrm{Hz}$ and 230V, 50Hz, 4-bit DPWM, 8-bit current A/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50         |

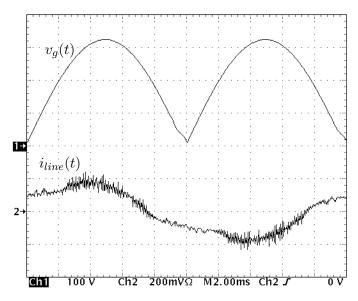

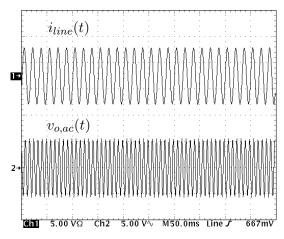

| 3.14 | Converter waveforms for very light load operation, $P=20\mathrm{W},V_{g,rms}=230\mathrm{V},50\mathrm{Hz},$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|      | 4-bit DPWM and current sensing A/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51         |

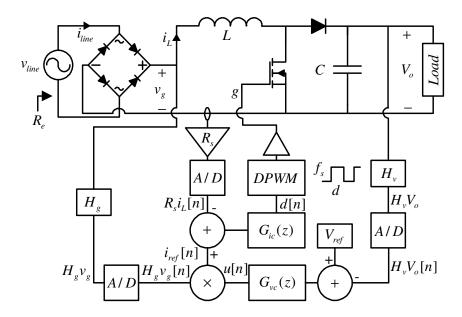

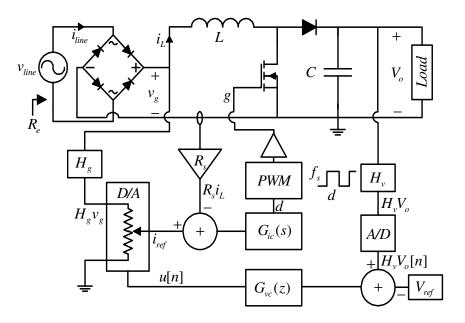

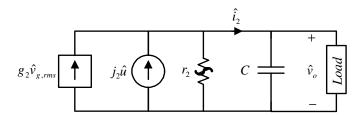

| 4.1  | DACM controlled PFC boost rectifier, $C = 220 \mu \text{F}$ , $L = 1.5 \text{mH}$ , $H_v = 1/250$ , $R_s =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |

| 1.1  | $1\Omega, V_{o,nominal} = 392V, f_s = 68kHz. \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.5        |

| 4.2  | DNLC controlled PFC boost rectifier, $C = 220\mu\text{F}$ , $L = 1.5\text{mH}$ , $H_v = 1/250$ , $R_s =$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <i>J</i> ( |

| 1.4  | $1\Omega, V_{o,nominal} = 392V, f_s = 68kHz. \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56         |

|      | $r_0, r_0, nominal = 0.02 r, j_S = 0.0 mag 1.0 mag 1.$ | 90         |

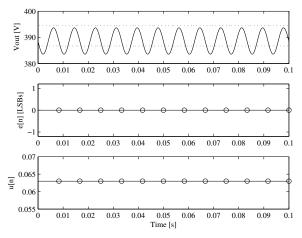

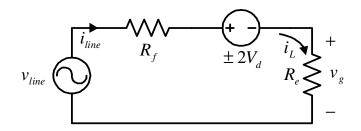

| large-signal model of an ideal rectifier output port, which appropri-                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

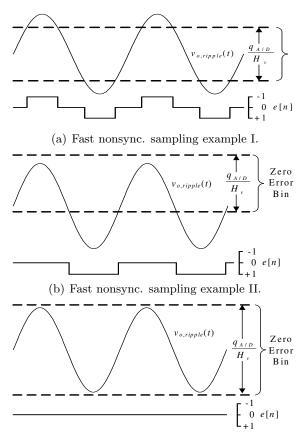

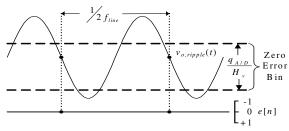

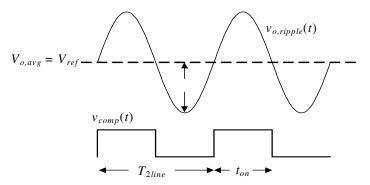

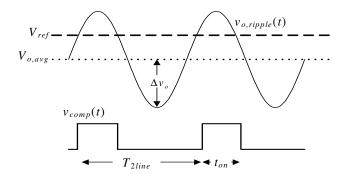

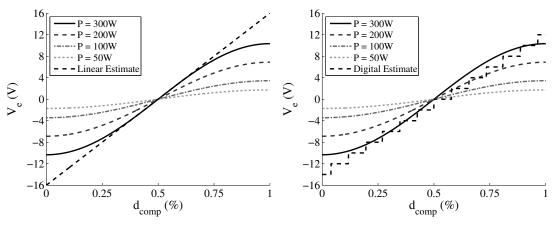

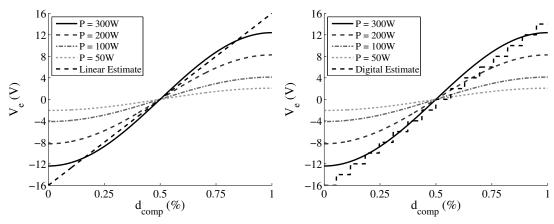

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|